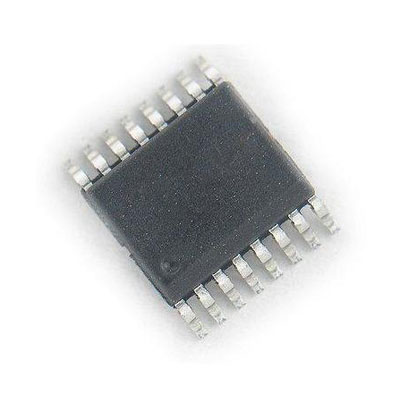

Counter Shift Registers 8-BIT SHIFT REGISTER

Las imágenes son sólo para referencia..

Consulte las Especificaciones del producto para obtener detalles del producto.

Counter Shift Registers 8-BIT SHIFT REGISTER

Los pedidos superiores a $200 son elegibles para un regalo de estilo chino de edición limitada.

Los pedidos superiores a $1000 califican para una exención de tarifa de envío de $30.

Los pedidos que superen los $5000 disfrutan de la exención de tarifas de envío y transacción.

Estas ofertas son aplicables tanto a clientes nuevos como existentes y son válidas desde el 1 de enero de 2024 hasta el 31 de diciembre de 2024..

NEXPERIA

74HC595DB,112 datasheet

SSOP-16

Ics lógicos

Envíe su solicitud de cotización ahora y esperamos brindarle una cotización dentro de mayo 04, 2024. Realice su pedido ahora y esperamos completar la transacción dentro de mayo 08, 2024. Ps: La hora es según GMT+8:00.

SAMSUNG

1 PCS

KHA884901X-MC13 .PDF

INTEL

1351 PCS

5M160ZE64C4N .PDF

XILINX

611 PCS

XC3S200-4FT256I .PDF

TI

1343 PCS

TPS65100QPWPRQ1 .PDF

2024-05-03

Known Tony for years... One of the best of the best... Honest & Reliable.... Thanks Tony...

2024-05-03

Lulu is very professional... I feel that she actually cares about her business and her customers. I will definitely do business with her again.

2024-05-02

MICKEY CAME THROUGH FOR US (ONE MORE TIME) !! GOOD GUYS!!

2024-05-02

Nice Business

2024-05-02

CENSTRY is a great company to work with

2024-05-01

Outstanding service!!

2024-04-30

Censtry and his teams are very professional,efficient, always fast quote and shipment, great company

2024-04-27

Preffered, Trusted Source

2024-04-22

Prompt shipment

2024-04-11

quite good deal. professional partners. Thank you Yoram and Dan, expecting more business together

Valoramos mucho sus comentarios. Comparta su reseña más genuina.

*Por favor, inicie sesión en su cuenta antes de publicar un comentario