Clock Drivers & Distribution ISP 0 Delay Unv Fan- Out Buf-Sngl End I

Las imágenes son sólo para referencia..

Consulte las Especificaciones del producto para obtener detalles del producto.

Clock Drivers & Distribution ISP 0 Delay Unv Fan- Out Buf-Sngl End I

Los pedidos superiores a $200 son elegibles para un regalo de estilo chino de edición limitada.

Los pedidos superiores a $1000 califican para una exención de tarifa de envío de $30.

Los pedidos que superen los $5000 disfrutan de la exención de tarifas de envío y transacción.

Estas ofertas son aplicables tanto a clientes nuevos como existentes y son válidas desde el 1 de enero de 2024 hasta el 31 de diciembre de 2024..

Lattice

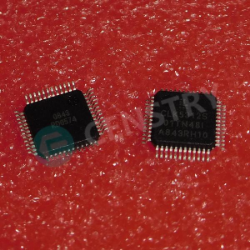

ISPPAC-CLK5312S-01TN48I datasheet

QFP-48

Reloj y temporizador Ics

Envíe su solicitud de cotización ahora y esperamos brindarle una cotización dentro de mayo 03, 2024. Realice su pedido ahora y esperamos completar la transacción dentro de mayo 08, 2024. Ps: La hora es según GMT+8:00.

Lattice

265 PCS

PALCE29M16H-25JC .PDF

Lattice

274 PCS

PALCE29M16H25JC .PDF

Lattice

1609 PCS

PALCE22V10H-25JI/4 .PDF

Lattice

4 PCS

PALCE22V10H-15PC/5 .PDF

2024-05-02

very fast thanks

2024-05-02

Fast shipping

2024-05-02

Goods arrived and work perfectly.

2024-05-01

impossible to find, except here.

2024-04-30

TRANSISTORS ARE GOOD

2024-04-27

Mercancía correcta. Envío rápido. Muy satisfecho.

2024-04-22

Censtry elec = Good company, happy business

2024-04-11

We highly recommend Pinewood Electronics Ltd and are looking forward to our next deal. Darren is very professional and our order was shipped promptly and the parts were good quality.

2024-03-21

Good supplier !i will buy it again ,Nice

2024-02-07

Very proffessional and reliable company. Was a pleasure for me to work with Mara.

Valoramos mucho sus comentarios. Comparta su reseña más genuina.

*Por favor, inicie sesión en su cuenta antes de publicar un comentario